# Programming Persistent Memory

A Comprehensive Guide for Developers

Steve Scargall

# Programming Persistent Memory

A Comprehensive Guide for Developers

**Steve Scargall**

#### Programming Persistent Memory: A Comprehensive Guide for Developers

Steve Scargall Santa Clara, CA, USA

#### ISBN-13 (pbk): 978-1-4842-4931-4 https://doi.org/10.1007/978-1-4842-4932-1

ISBN-13 (electronic): 978-1-4842-4932-1

#### Copyright © 2020 by Intel

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

**Open Access** This book is licensed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give

appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this book are included in the book's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the book's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

Trademarked names, logos, and images may appear in this book. Rather than use a trademark symbol with every occurrence of a trademarked name, logo, or image we use the names, logos, and images only in an editorial fashion and to the benefit of the trademark owner, with no intention of infringement of the trademark.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Managing Director, Apress Media LLC: Welmoed Spahr Acquisitions Editor: Susan McDermott Development Editor: Laura Berendson Coordinating Editor: Jessica Vakili

Distributed to the book trade worldwide by Springer Science+Business Media New York, 233 Spring Street, 6th Floor, New York, NY 10013. Phone 1-800-SPRINGER, fax (201) 348-4505, e-mail orders-ny@springer-sbm.com, or visit www.springeronline.com. Apress Media, LLC is a California LLC and the sole member (owner) is Springer Science + Business Media Finance Inc (SSBM Finance Inc). SSBM Finance Inc is a **Delaware** corporation.

For information on translations, please e-mail rights@apress.com, or visit http://www.apress.com/rights-permissions.

Apress titles may be purchased in bulk for academic, corporate, or promotional use. eBook versions and licenses are also available for most titles. For more information, reference our Print and eBook Bulk Sales web page at http://www.apress.com/bulk-sales.

Any source code or other supplementary material referenced by the author in this book is available to readers on GitHub via the book's product page, located at www.apress.com/978-1-4842-4931-4. For more detailed information, please visit http://www.apress.com/source-code.

Printed on acid-free paper

# **Table of Contents**

| About the Author                                         | xiii  |

|----------------------------------------------------------|-------|

| About the Technical Reviewer                             | xv    |

| About the Contributors                                   | xvii  |

| Acknowledgments                                          | xxi   |

| Preface                                                  | xxiii |

| Chapter 1: Introduction to Persistent Memory Programming | 1     |

| A High-Level Example Program                             | 2     |

| What's Different?                                        | 5     |

| The Performance Difference                               | 6     |

| Program Complexity                                       | 7     |

| How Does libpmemkv Work?                                 |       |

| What's Next?                                             | 9     |

| Summary                                                  | 9     |

| Chapter 2: Persistent Memory Architecture                | 11    |

| Persistent Memory Characteristics                        | 12    |

| Platform Support for Persistent Memory                   | 13    |

| Cache Hierarchy                                          | 14    |

| Power-Fail Protected Domains                             | 16    |

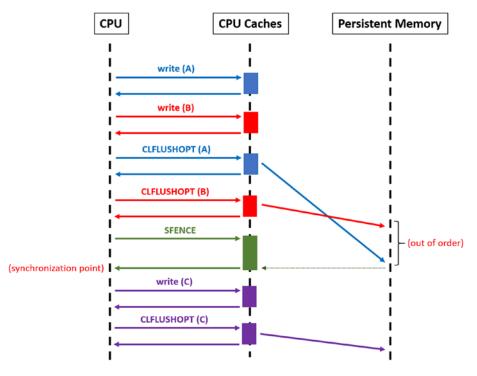

| The Need for Flushing, Ordering, and Fencing             | 19    |

| Data Visibility                                          | 23    |

| Intel Machine Instructions for Persistent Memory         |       |

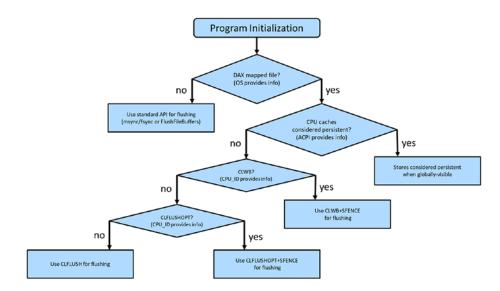

| Detecting Platform Capabilities                          | 25    |

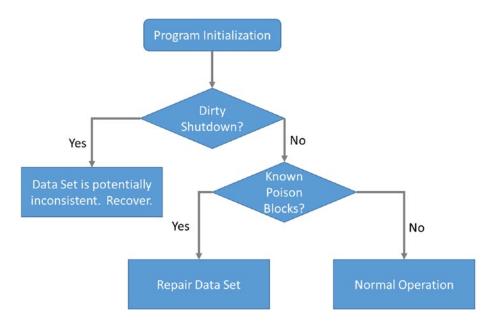

| Application Startup and Recovery                                 | 27 |

|------------------------------------------------------------------|----|

| What's Next?                                                     | 29 |

| Summary                                                          | 29 |

| Chapter 3: Operating System Support for Persistent Memory        | 31 |

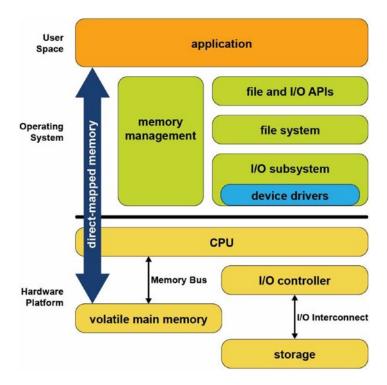

| Operating System Support for Memory and Storage                  | 31 |

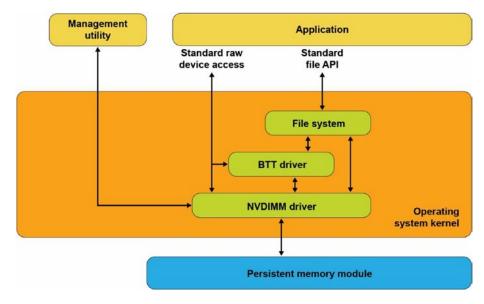

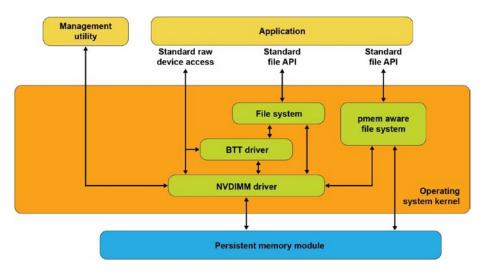

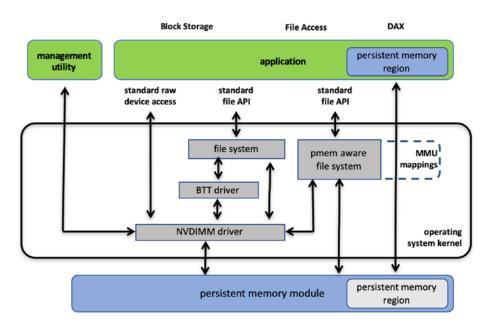

| Persistent Memory As Block Storage                               | 33 |

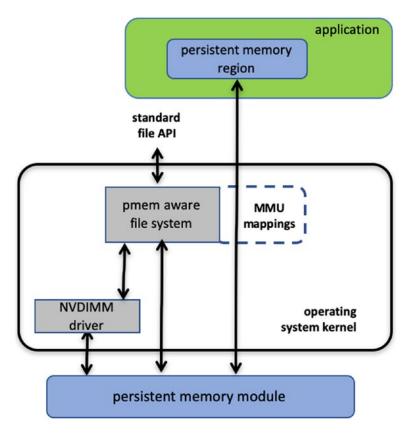

| Persistent Memory-Aware File Systems                             | 34 |

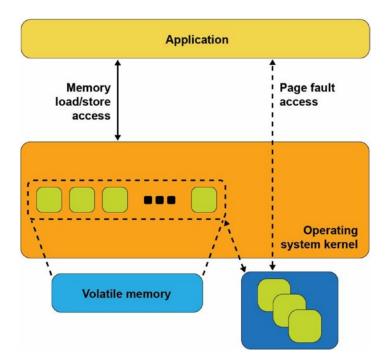

| Memory-Mapped Files                                              | 35 |

| Persistent Memory Direct Access (DAX)                            | 43 |

| Summary                                                          | 53 |

| Chapter 4: Fundamental Concepts of Persistent Memory Programming | 55 |

| What's Different?                                                | 55 |

| Atomic Updates                                                   | 56 |

| Transactions                                                     | 57 |

| Atomicity                                                        | 57 |

| Consistency                                                      | 58 |

| Isolation                                                        | 58 |

| Durability                                                       | 58 |

| Flushing Is Not Transactional                                    | 59 |

| Start-Time Responsibilities                                      | 59 |

| Tuning for Hardware Configurations                               | 60 |

| Summary                                                          | 60 |

| Chapter 5: Introducing the Persistent Memory Development Kit     | 63 |

| Background                                                       | 63 |

| Choosing the Right Semantics                                     | 64 |

| Volatile Libraries                                               | 65 |

| libmemkind                                                       | 65 |

| libvmemcache                                                     | 66 |

| libvmem                                                          | 67 |

| Persistent Libraries                                       | 67 |

|------------------------------------------------------------|----|

| libpmem                                                    | 67 |

| libpmemobj                                                 | 68 |

| libpmemobj-cpp                                             |    |

| libpmemkv                                                  | 69 |

| libpmemlog                                                 | 69 |

| libpmemblk                                                 | 69 |

| Tools and Command Utilities                                | 70 |

| pmempool                                                   | 70 |

| pmemcheck                                                  | 70 |

| pmreorder                                                  | 71 |

| Summary                                                    | 71 |

| Chapter 6: libpmem: Low-Level Persistent Memory Support    | 73 |

| Using the Library                                          | 74 |

| Mapping a File                                             | 75 |

| Copying to Persistent Memory                               |    |

| Separating the Flush Steps                                 |    |

| Summary                                                    |    |

| Chapter 7: libpmemobj: A Native Transactional Object Store |    |

| What is libpmemobj?                                        |    |

| Why not malloc()?                                          |    |

| Grouping Operations                                        |    |

| Memory Pools                                               |    |

| Creating Memory Pools                                      |    |

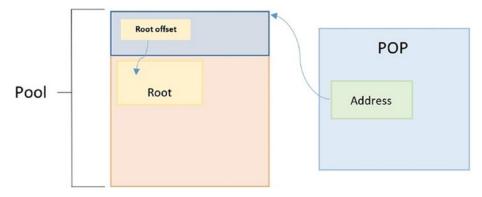

| Pool Object Pointer (POP) and the Root Object              |    |

| Opening and Reading from Memory Pools                      |    |

| Memory Poolsets                                            |    |

| Concatenated Poolsets                                      |    |

| Replica Poolsets                                           |    |

| Managing Memory Pools and Poolsets                         |    |

| Typed Object Identifiers (TOIDs)                                                              |       |

|-----------------------------------------------------------------------------------------------|-------|

| Allocating Memory                                                                             |       |

| Persisting Data                                                                               |       |

| Atomic Operations                                                                             |       |

| Reserve/Publish API                                                                           |       |

| Transactional API                                                                             | 100   |

| Optional Flags                                                                                | 104   |

| Persisting Data Summary                                                                       | 104   |

| Guarantees of libpmemobj's APIs                                                               | 105   |

| Managing Library Behavior                                                                     |       |

| Debugging and Error Handling                                                                  |       |

| Summary                                                                                       | 108   |

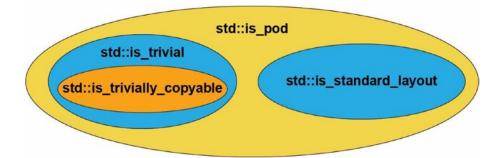

| Chapter 8: libpmemobj-cpp: The Adaptable Language - C++                                       | - and |

| Persistent Memory                                                                             |       |

| Introduction                                                                                  |       |

|                                                                                               |       |

| Metaprogramming to the Rescue                                                                 |       |

| Metaprogramming to the Rescue<br>Persistent Pointers                                          |       |

|                                                                                               |       |

| Persistent Pointers                                                                           |       |

| Persistent Pointers<br>Transactions                                                           |       |

| Persistent Pointers<br>Transactions<br>Snapshotting                                           |       |

| Persistent Pointers<br>Transactions<br>Snapshotting<br>Allocating.                            |       |

| Persistent Pointers<br>Transactions<br>Snapshotting<br>Allocating<br>C++ Standard limitations |       |

| Limitations Summary               |  |

|-----------------------------------|--|

| Persistence Simplified            |  |

| The Ecosystem                     |  |

| Persistent Containers             |  |

| Examples of Persistent Containers |  |

| Summary                           |  |

| Chapter 9: pmemkv: A Persistent In-Memory Key-Value Store                                   |     |

|---------------------------------------------------------------------------------------------|-----|

| pmemkv Architecture                                                                         | 143 |

| A Phonebook Example                                                                         | 147 |

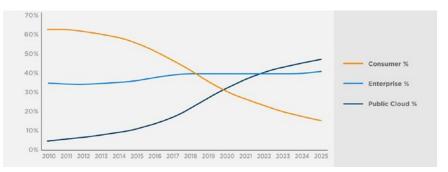

| Bringing Persistent Memory Closer to the Cloud                                              | 151 |

| Summary                                                                                     | 152 |

| Chapter 10: Volatile Use of Persistent Memory                                               | 155 |

| Introduction                                                                                | 155 |

| Background                                                                                  | 156 |

| Memory Allocation                                                                           | 156 |

| How it Works                                                                                | 156 |

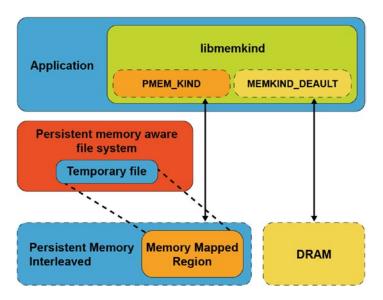

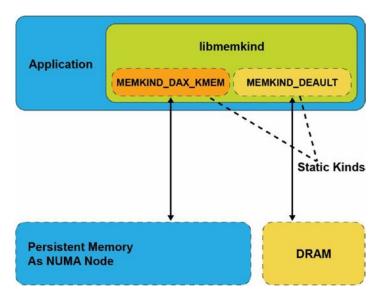

| Supported "Kinds" of Memory                                                                 | 157 |

| The memkind API                                                                             | 159 |

| Kind Management API                                                                         | 159 |

| Heap Management API                                                                         | 164 |

| Kind Configuration Management                                                               | 167 |

| Additional memkind Code Examples                                                            | 168 |

| C++ Allocator for PMEM Kind                                                                 | 168 |

| pmem::allocator methods                                                                     | 169 |

| Nested Containers                                                                           | 169 |

| C++ Examples                                                                                | 170 |

| Using the pmem::allocator                                                                   | 170 |

| Creating a Vector of Strings                                                                | 171 |

| Expanding Volatile Memory Using Persistent Memory                                           | 173 |

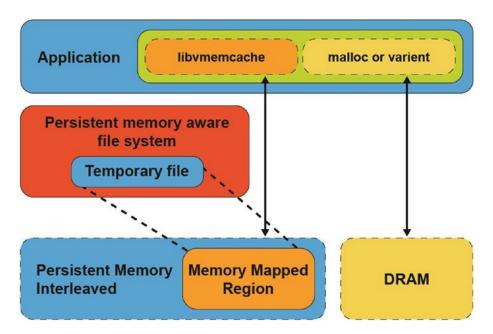

| libvmemcache: An Efficient Volatile Key-Value Cache for Large-Capacity<br>Persistent Memory | 177 |

| libvmemcache Overview                                                                       |     |

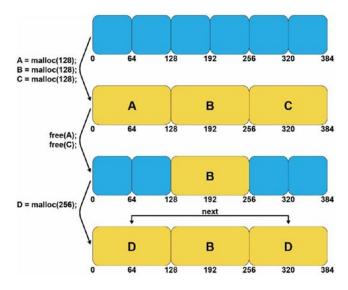

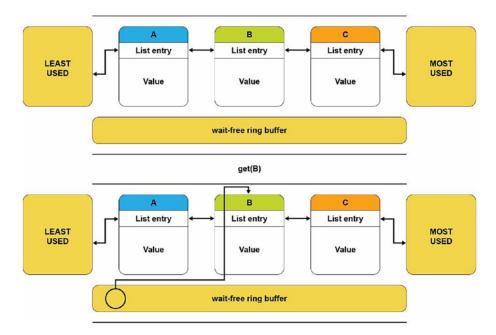

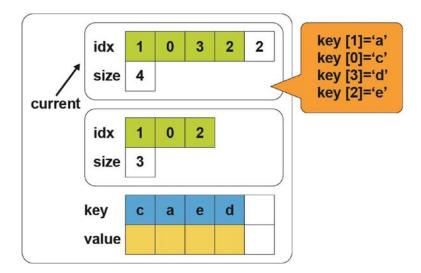

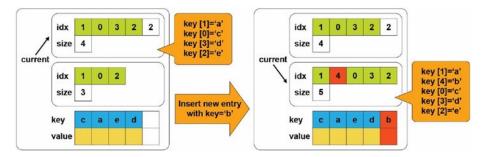

| libvmemcache Design                                                                         | 180 |

| Using libvmemcache                                                                          | 183 |

| Summary                                                                                     | 186 |

| Chapter 11: Designing Data Structures for Persistent Memory     | 187 |

|-----------------------------------------------------------------|-----|

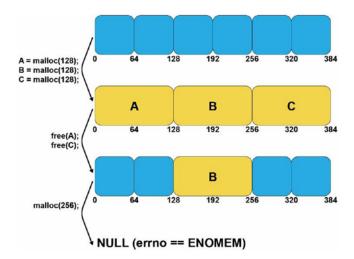

| Contiguous Data Structures and Fragmentation                    |     |

| Internal and External Fragmentation                             |     |

| Atomicity and Consistency                                       |     |

| Selective Persistence                                           | 193 |

| Example Data Structures                                         | 193 |

| Summary                                                         | 206 |

| Chapter 12: Debugging Persistent Memory Applications            | 207 |

| pmemcheck for Valgrind                                          | 208 |

| Stack Overflow Example                                          | 208 |

| Memory Leak Example                                             | 209 |

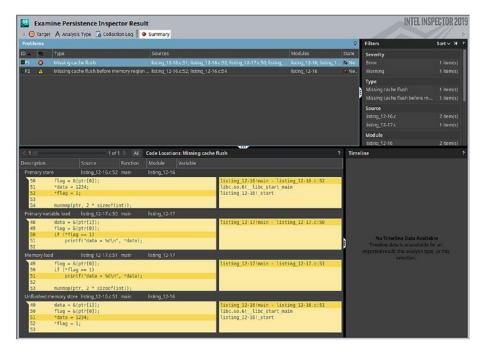

| Intel Inspector – Persistence Inspector                         | 210 |

| Stack Overflow Example                                          |     |

| Memory Leak Example                                             | 212 |

| Common Persistent Memory Programming Problems                   |     |

| Nonpersistent Stores                                            |     |

| Stores Not Added into a Transaction                             | 228 |

| Memory Added to Two Different Transactions                      | 233 |

| Memory Overwrites                                               | 240 |

| Unnecessary Flushes                                             | 242 |

| Out-of-Order Writes                                             | 247 |

| Summary                                                         | 259 |

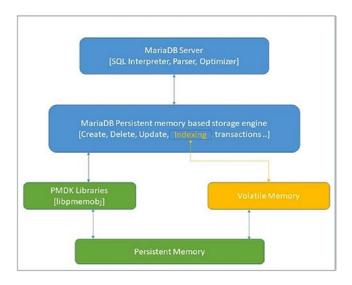

| Chapter 13: Enabling Persistence Using a Real-World Application | 261 |

| The Database Example                                            |     |

| Different Persistent Memory Enablement Approaches               |     |

| Developing a Persistent Memory-Aware MariaDB* Storage Engine    | 263 |

| Understanding the Storage Layer                                 |     |

| Creating a Storage Engine Class                                 | 265 |

| Summary                                                         |     |

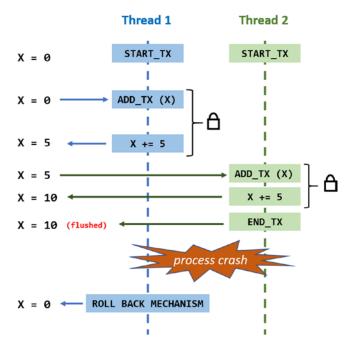

| Chapter 14: Concurrency and Persistent Memory                  |     |

|----------------------------------------------------------------|-----|

| Transactions and Multithreading                                |     |

| Mutexes on Persistent Memory                                   |     |

| Atomic Operations and Persistent Memory                        |     |

| Lock-Free Algorithms and Persistent Memory                     |     |

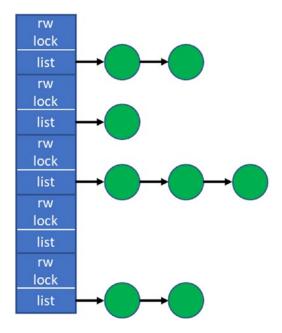

| Concurrent Data Structures for Persistent Memory               |     |

| Concurrent Ordered Map                                         |     |

| Concurrent Hash Map                                            | 291 |

| Summary                                                        |     |

| Chapter 15: Profiling and Performance                          | 295 |

| Introduction                                                   |     |

| Performance Analysis Concepts                                  |     |

| Compute-Bound vs. Memory-Bound                                 | 295 |

| Memory Latency vs. Memory Capacity                             |     |

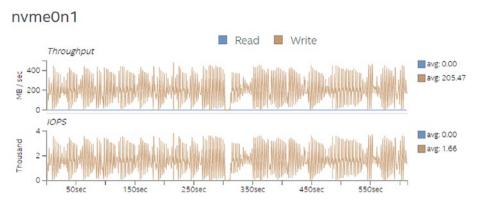

| Read vs. Write Performance                                     |     |

| Memory Access Patterns                                         | 296 |

| I/O Storage Bound Workloads                                    | 297 |

| Determining the Suitability of Workloads for Persistent Memory | 297 |

| Volatile Use Cases                                             |     |

| Use Cases Requiring Persistence                                | 301 |

| Performance Analysis of Workloads Using Persistent Memory      |     |

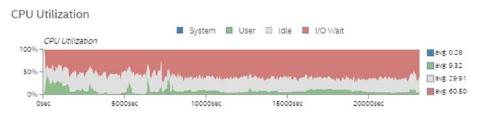

| Characterizing the Workload                                    | 303 |

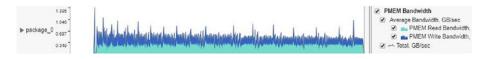

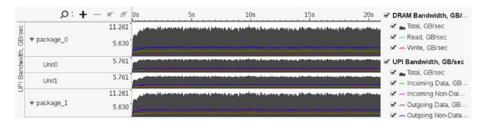

| Memory Bandwidth and Latency                                   | 303 |

| Persistent Memory Read-Write Ratio                             | 305 |

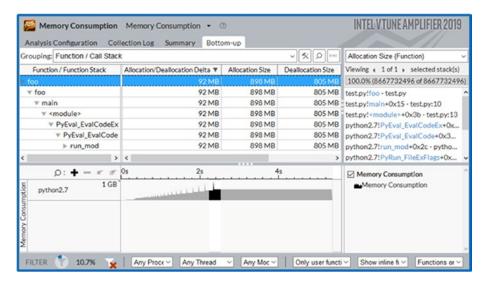

| Working Set Size and Memory Footprint                          | 305 |

| Non-Uniform Memory Architecture (NUMA) Behavior                |     |

| Optimizing the Software for Persistent Memory                  |     |

| Summary                                                        |     |

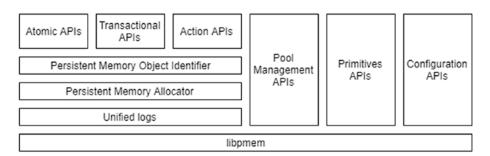

| Chapter 16: PMDK Internals: Important Algorithms and Data Structures                | 313 |

|-------------------------------------------------------------------------------------|-----|

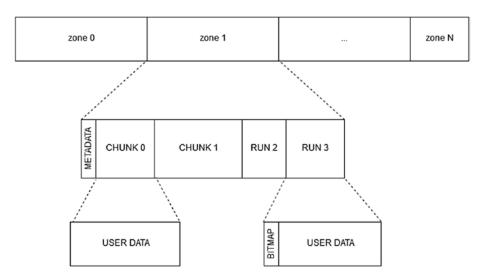

| A Pool of Persistent Memory: High-Level Architecture Overview                       | 313 |

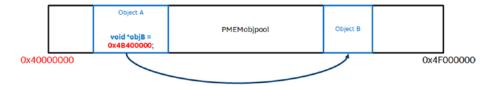

| The Uncertainty of Memory Mapping: Persistent Memory Object Identifier              | 315 |

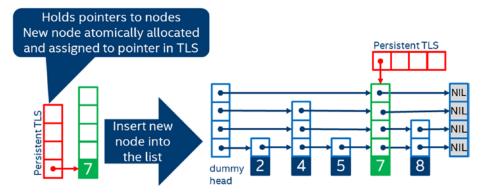

| Persistent Thread Local Storage: Using Lanes                                        | 318 |

| Ensuring Power-Fail Atomicity: Redo and Undo Logging                                | 320 |

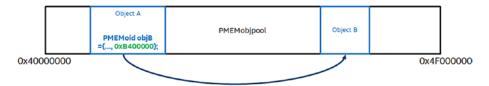

| Transaction Redo Logging                                                            | 320 |

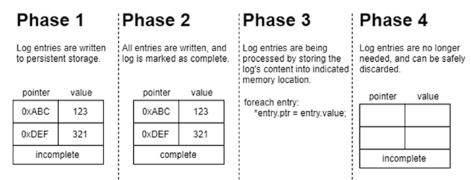

| Transaction Undo Logging                                                            | 321 |

| libpmemobj Unified Logging                                                          | 322 |

| Persistent Allocations: The Interface of a Transactional Persistent Allocator       | 323 |

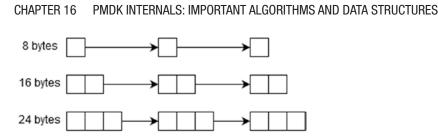

| Persistent Memory Heap Management: Allocator Design for Persistent Memory           | 324 |

| ACID Transactions: Efficient Low-Level Persistent Transactions                      | 328 |

| Lazy Reinitialization of Variables: Storing the Volatile State on Persistent Memory | 330 |

| Summary                                                                             | 331 |

| Chapter 17: Reliability, Availability, and Serviceability (RAS)                     | 333 |

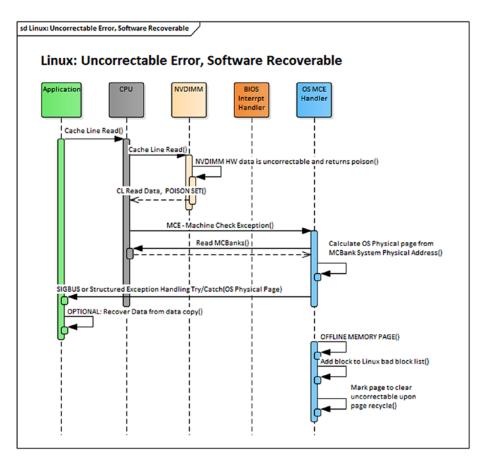

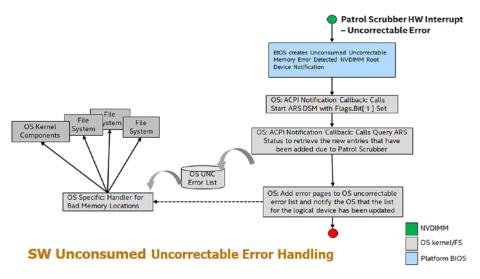

| Dealing with Uncorrectable Errors                                                   | 333 |

| Consumed Uncorrectable Error Handling                                               | 334 |

| Unconsumed Uncorrectable Error Handling                                             | 336 |

| Clearing Uncorrectable Errors                                                       | 339 |

| Device Health                                                                       | 339 |

| ACPI-Defined Health Functions (_NCH, _NBS)                                          | 342 |

| Vendor-Specific Device Health (_DSMs)                                               | 342 |

| ACPI NFIT Health Event Notification                                                 | 343 |

| Unsafe/Dirty Shutdown                                                               | 343 |

| Application Utilization of Data Loss Count (DLC)                                    | 344 |

| Summary                                                                             | 346 |

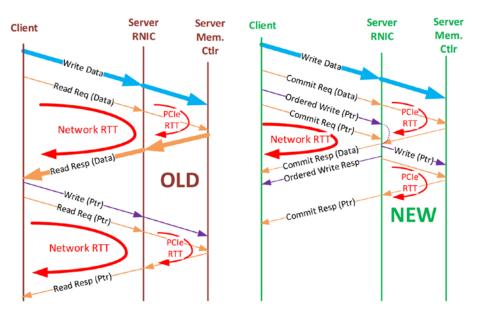

| Chapter 18: Remote Persistent Memory                                                | 347 |

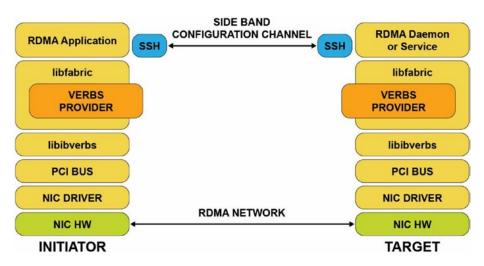

| RDMA Networking Protocols                                                           | 348 |

| Goals of the Initial Remote Persistent Memory Architecture                          | 351 |

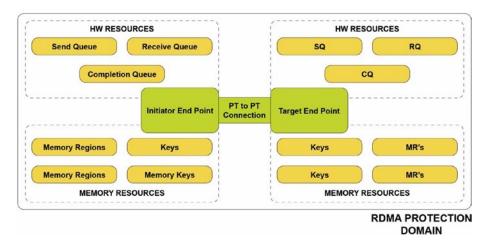

| Guaranteeing Remote Persistence                                                     | 351 |

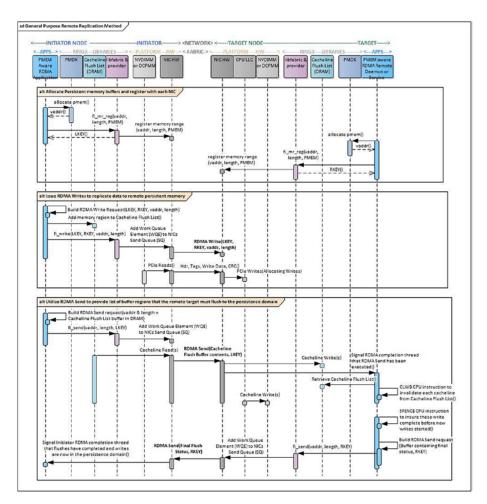

| General-Purpose Remote Replication Method                                           | 353 |

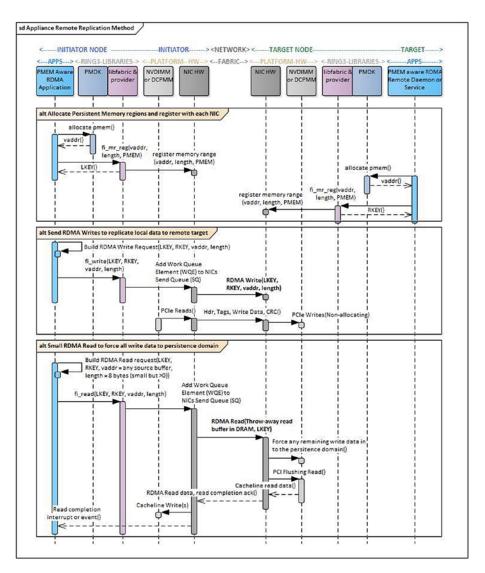

| Appliance Remote Replication Method                                         | 355 |

|-----------------------------------------------------------------------------|-----|

| General Software Architecture                                               | 357 |

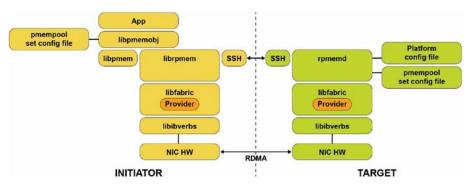

| librpmem Architecture and Its Use in Replication                            | 358 |

| Configuring Remote Replication Using Poolsets                               | 362 |

| Performance Considerations                                                  | 362 |

| Remote Replication Error Handling                                           | 364 |

| Say Hello to the Replicated World                                           | 364 |

| Summary                                                                     | 370 |

| Chapter 19: Advanced Topics                                                 | 373 |

| Nonuniform Memory Access (NUMA)                                             | 373 |

| NUMACTL Linux Utility                                                       | 374 |

| NDCTL Linux Utility                                                         | 376 |

| Intel Memory Latency Checker Utility                                        | 378 |

| NUMASTAT Utility                                                            | 380 |

| Intel VTune Profiler – Platform Profiler                                    | 381 |

| IPMCTL Utility                                                              | 381 |

| BIOS Tuning Options                                                         | 382 |

| Automatic NUMA Balancing                                                    | 382 |

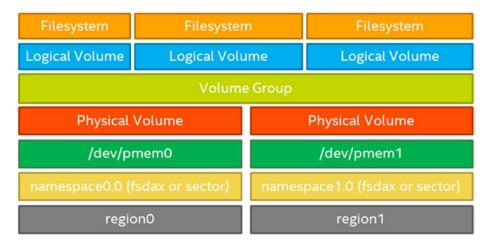

| Using Volume Managers with Persistent Memory                                | 383 |

| The mmap() MAP_SYNC Flag                                                    | 385 |

| Summary                                                                     |     |

| Appendix A: How to Install NDCTL and DAXCTL on Linux                        | 389 |

| Prerequisites                                                               | 389 |

| Installing NDCTL and DAXCTL Using the Linux Distribution Package Repository | 390 |

| Searching for Packages Within a Package Repository                          | 391 |

| Installing NDCTL and DAXCTL from the Package Repository                     | 392 |

| Appendix B: How to Install the Persistent Memory Development Kit (PMDK) | <mark>395</mark>      |

|-------------------------------------------------------------------------|-----------------------|

| PMDK Prerequisites                                                      | 395                   |

| Installing PMDK Using the Linux Distribution Package Repository         | 395                   |

| Package Naming Convention                                               | 396                   |

| Searching for Packages Within a Package Repository                      | 396                   |

| Installing PMDK Libraries from the Package Repository                   | <mark>398</mark>      |

| Installing PMDK on Microsoft Windows                                    | 402                   |

| Appendix C: How to Install IPMCTL on Linux and Windows                  | . <mark>. 40</mark> 3 |

| IPMCTL Linux Prerequisites                                              | 404                   |

| libsafec                                                                | 404                   |

| IPMCTL Linux Packages                                                   | 404                   |

| IPMCTL for Microsoft Windows                                            | 404                   |

| Using ipmctl                                                            | 405                   |

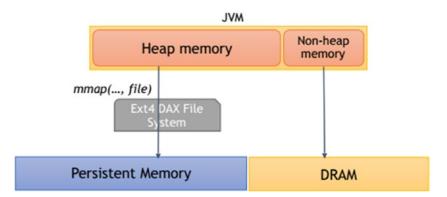

| Appendix D: Java for Persistent Memory                                  | . 411                 |

| Volatile Use of Persistent Memory                                       | 411                   |

| Heap Allocation on Alternative Memory Devices                           | 412                   |

| Persistent Collections for Java (PCJ)                                   | 416                   |

| Using PCJ in Java Applications                                          | 417                   |

| Low-Level Persistent Library (LLPL)                                     | 418                   |

| Using LLPL in Java Applications                                         | 419                   |

| Summary                                                                 | 419                   |

| Appendix E: The Future of Remote Persistent Memory Replication          | 421                   |

| Glossary                                                                | 425                   |

| Index                                                                   | 429                   |

# **About the Author**

**Steve Scargall** is a persistent memory software and cloud architect at Intel Corporation. As a technology evangelist, he supports the enabling and development effort to integrate persistent memory technology into software stacks, applications, and hardware architectures. This includes working with independent software vendors (ISVs) on both proprietary and open source development, original equipment manufacturers (OEMs), and cloud service providers (CSPs).

Steve holds a Bachelor of Science in computer science and cybernetics from the University of Reading, UK, where he studied neural networks, AI, and robotics. He has over 19 years' experience providing performance analysis on x86 architecture and SPARC for Solaris Kernel, ZFS, and UFS file system. He performed DTrace debugging in enterprise and cloud environments during his tenures at Sun Microsystems and Oracle.

# **About the Technical Reviewer**

Andy Rudoff is a principal engineer at Intel Corporation, focusing on non-volatile memory programming. He is a contributor to the SNIA NVM Programming Technical Work Group. His more than 30 years' industry experience includes design and development work in operating systems, file systems, networking, and fault management at companies large and small, including Sun Microsystems and VMware. Andy has taught various operating systems classes over the years and is a coauthor of the popular *UNIX Network Programming* textbook.

# **About the Contributors**

**Piotr Balcer** is a software engineer at Intel Corporation with many years' experience working on storage-related technologies. He holds a Bachelor of Science in engineering from the Gdańsk University of Technology, Poland, where he studied system software engineering. Piotr has been working on the software ecosystem for next-generation persistent memory since 2014.

**Eduardo Berrocal** joined Intel Corporation as a cloud software engineer in 2017 after receiving his PhD in computer science from the Illinois Institute of Technology. His doctoral research focused on data analytics and fault tolerance for high-performance computing. Past experience includes working as an intern at Bell Labs (Nokia), a research aid at Argonne National Laboratory, a scientific programmer and web developer at the University of Chicago, and an intern in the CESVIMA laboratory in Spain.

Adam Borowski is a software engineer at Intel Corporation, hailing from the University of Warsaw, Poland. He is a Debian developer and has made many open source contributions over the past two decades. Adam is currently working on persistent memory stacks, both on upstream code and integrating it with downstream distributions.

**Igor Chorazewicz** is a software engineer at Intel Corporation. His main focus is on persistent memory data structures and enabling C++ applications for persistent memory. Igor holds a Bachelor of Science in engineering from the Gdańsk University of Technology, Poland.

Adam Czapski is a technical writer at Intel Corporation. He writes technical documentation in the Data Center Group and is currently working in the persistent memory department. Adam holds a Bachelor of Arts in English philology and a master's degree in natural language processing from the Gdańsk University of Technology, Poland.

**Steve Dohrmann** is a software engineer at Intel Corporation. He has worked on a variety of projects over the past 20 years, including media frameworks, mobile agent software, secure collaboration software, and parallel programming language implementation. He is currently working on enabling the use of persistent memory in Java\*.

#### ABOUT THE CONTRIBUTORS

**Chet Douglas** is a principal software engineer at Intel Corporation and focuses on cloud software architecture along with operating system and OEM enabling of non-volatile memory technologies. He has over 14 years' experience working on various enterprise and client programs and 28 years of total storage experience. Chet has worked in all aspects of storage, including storage controller hardware design, SCSI disk/tape/CD writer firmware architecture, storage management software architecture, Microsoft Windows\* and Linux kernel-mode drivers, enterprise hardware RAID, and client/ workstation software RAID. He holds seven storage-related hardware and software patents and has a dual Bachelor of Science in electrical engineering and computer engineering from Clarkson University, New York.

**Ken Gibson** is the director of persistent memory software architecture within Intel Corporation's Data Center Group. Since 2012, Ken and his team have been working with Intel's server and software partners to create the open persistent memory programming model.

**Tomasz Gromadzki** is a software architect in Intel Corporation's Non-Volatile Memory Solutions Group. His focus is on remote persistent memory access, which includes proper integration of persistent memory with other (networking) technologies as well as optimal persistent memory replication procedures and algorithms.

**Kishor Kharbas** is a software engineer on the Java runtime engineering team at Intel Corporation. For the past eight years, he has been working to optimize Oracle's OpenJDK on Intel platforms. This involves Java garbage collection and compiler back-end optimization.

**Jackson Marusarz** is a senior technical consulting engineer (TCE) in Intel Corporation's Compute Performance and Developer Products Division. As the lead TCE for Intel VTune Profiler, his main focus is on software performance analysis and tuning for both serial and multithreaded applications. Jackson's time is split between determining how to analyze and tune software and creating tools that help others do the same.

**Jan Michalski** is a software engineer in Intel Corporation's Non-Volatile Memory Solutions Group. His focus is on remote persistent memory access, which includes proper integration of persistent memory with other technologies, as well as looking for optimal persistent memory replication procedures and algorithms. He holds a master's degree in computer engineering from the Gdańsk University of Technology, Poland, where he studied system software engineering. **Nicholas Moulin** is a cloud software architect at Intel Corporation. Since joining Intel in 2012, he has focused on enabling and developing persistent memory software for operating systems and platform firmware and managing persistent memory hardware. Nicholas is currently working with industry partners to define and improve RAS features relevant to the persistent memory programming model.

**Szymon Romik** is a software engineer at Intel Corporation and is currently focused on persistent memory programming. He previously worked as a lead software engineer on 5G technologies at Ericsson. Szymon holds a master's degree in mathematics from Jagiellonian University, Poland.

**Jakub Schmiegel** is a software architect in Intel Corporation's Non-Volatile Memory Solutions Group where he has been focused on enabling existing applications to persistent memory and analyzing their performance for more than four years. Jakub holds a master's degree in computer science from the Gdańsk University of Technology, Poland.

**Kevin Shalkowsky** is a Telly Award–winning creative director, graphic designer, and animator with more than a decade of experience. While his contributions are in technology today, Kevin has spent time in broadcast journalism and selling numerous products through 30-minute late-night infomercials. He resides in Oregon with his wife and son. From time to time, you can find Kevin lost in the woods, lost in a parking lot, or lost in his design process – but this somehow got him to where he is today, and he wouldn't have it any other way.

**Vineet Singh** is a memory and storage tools software engineer at Intel Corporation. He develops techniques to help developers adapt to the latest memory technologies. Vineet holds a PhD in philosophy from the University of California and has a Bachelor of Technology degree from the Indian Institute of Information Technology, Design, and Manufacturing in Jabalpur.

**Pawel Skowron** is a software engineering manager at Intel Corporation with 20 years' experience in the software industry. Pawel has worked in various roles related to the whole-software development life cycle. His software engineering background lies in the areas of embedded systems, database systems, and applications. For the past few years, Pawel has led the development and validation of the Persistent Memory Development Kit (https://github.com/pmem/pmdk).

#### ABOUT THE CONTRIBUTORS

**Usha Upadhyayula** has been with Intel Corporation for 20 years serving in many different roles. Usha holds a master's degree in computer science from the University of South Carolina, and she spent the first few years at Intel developing user-level applications in C and C++. She later moved to customer-enabling roles for Intel media processors and support for Intel RAID software. Usha is currently part of the Data Center Group where she is focused on enabling cloud service providers to fully utilize and accelerate the adoption of Intel persistent memory products.

**Sergey Vinogradov** is a senior software development engineer at Intel Corporation where he spent more than seven years working on performance profiling tools and threading runtime libraries. During the past four years, Sergey has been working on C++ programming models and performance profiling methodologies for persistent memory.

# Acknowledgments

First and foremost, I would like to thank Ken Gibson for masterminding this book idea and for gifting me the pleasure of writing and managing it. Your support, guidance, and contributions have been instrumental in delivering a high-quality product.

If the Vulcan mind-meld or *The Matrix* Headjack were possible, I could have cloned Andy Rudoff's mind and allowed him to work on his daily activities. Instead, Andy's infinite knowledge of persistent memory had to be tapped through good old verbal communication and e-mail. I sincerely thank you for devoting so much time to me and this project. The results read for themselves.

Debbie Graham was instrumental in helping me manage this colossal project. Her dedication and support helped drive the project to an on-time completion.

To my friends and colleagues at Intel who contributed content, supported discussions, helped with decision-making, and reviewed drafts during the book-writing process. These are the real heroes. Without your heavily invested time and support, this book would have taken considerably longer to complete. It is a much better product as a result of the collaborative effort. A huge thanks to all of you.

I'd like to express my sincerest gratitude and appreciation to the people at Apress, without whom this book could not have been published. From the initial contact and outline discussions through the entire publishing process to this final polished product, the Apress team delivered continuous support and assistance. Many thanks to Susan, Jessica, and Rita. It was a real pleasure working with you.

# Preface

# **About This Book**

Persistent memory is often referred to as non-volatile memory (NVM) or storage class memory (SCM). In this book, we purposefully use *persistent memory* as an all-encompassing term to represent all the current and future memory technologies that fall under this umbrella. This book introduces the persistent memory technology and provides answers to key questions. For software developers, those questions include: What is persistent memory? How do I use it? What APIs and libraries are available? What benefits can it provide for my application? What new programming methods do I need to learn? How do I design applications to use persistent memory? Where can I find information, documentation, and help?

System and cloud architects will be provided with answers to questions such as: What is persistent memory? How does it work? How is it different than DRAM or SSD/ NVMe storage devices? What are the hardware and operating system requirements? What applications need or could benefit from persistent memory? Can my existing applications use persistent memory without being modified?

Persistent memory is not a plug-and-play technology for software applications. Although it may look and feel like traditional DRAM memory, applications need to be modified to fully utilize the persistence feature of persistent memory. That is not to say that applications cannot run unmodified on systems with persistent memory installed, they can, but they will not see the full potential of what persistent memory offers without code modification.

Thankfully, server and operating system vendors collaborated very early in the design phase and already have products available on the market. Linux and Microsoft Windows already provide native support for persistent memory technologies. Many popular virtualization technologies also support persistent memory.

For ISVs and the developer community at large, the journey is just beginning. Some software has already been modified and is available on the market. However, it will take time for the enterprise and cloud computing industries to adopt and make the hardware available to the general marketplace. ISVs and software developers need time to understand what changes to existing applications are required and implement them.

#### PREFACE

To make the required development work easier, Intel developed and open sourced the Persistent Memory Development Kit (PMDK) available from https://pmem.io/ pmdk/. We introduce the PMDK in more detail in Chapter 5 and walk through most of the available libraries in subsequent chapters. Each chapter provides an in-depth guide so developers can understand what library or libraries to use. PMDK is a set of open source libraries and tools based on the Storage Networking Industry Association (SNIA) NVM programming model designed and implemented by over 50 industry partners. The latest NVM programming model document can be found at https://www.snia.org/ tech\_activities/standards/curr\_standards/npm. The model describes how software can utilize persistent memory features and enables designers to develop APIs that take advantage of NVM features and performance.

Available for both Linux and Windows, PMDK facilitates persistent memory programming adoption with higher-level language support. C and C++ support is fully validated. Support for other languages such as Java and Python is work in progress at the time this book was written. Other languages are expected to also adopt the programming model and provide native persistent memory APIs for developers. The PMDK development team welcomes and encourages new contributions to core code, new language bindings, or new storage engines for the persistent memory key-value store called pmemkv.

This book assumes no prior knowledge of persistent memory hardware devices or software development. The book layout allows you to freely navigate the content in the order you want. It is not required to read all chapters in order, though we do build upon concepts and knowledge described in previous chapters. In such cases, we make backward and forward references to relevant chapters and sections so you can learn or refresh your memory.

### **Book Structure**

This book has 19 chapters, each one focusing on a different topic. The book has three main sections. Chapters 1-4 provide an introduction to persistent memory architecture, hardware, and operating system support. Chapters 5-16 allow developers to understand the PMDK libraries and how to use them in applications. Finally, Chapters 17-19 provide information on advanced topics such as RAS and replication of data using RDMA.

- Chapter 1. Introduction to Persistent Memory *Introduces persistent memory and dips our toes in the water with a simple persistent key-value store example using libpmemkv.*

- Chapter 2. Persistent Memory Architecture *Describes the persistent memory architecture and focuses on the hardware requirements developers should know.*

- Chapter 3. Operating System Support for Persistent Memory Provides information relating to operating system changes, new features, and how persistent memory is seen by the OS.

- Chapter 4. Fundamental Concepts of Persistent Memory Programming – *Builds on the first three chapters and describes the fundamental concepts of persistent memory programming.*

- Chapter 5. Introducing the Persistent Memory Development Kit (PMDK) Introduces the Persistent Memory Development Kit (PMDK), a suite of libraries to assist software developers.

- Chapter 6. libpmem: Low-Level Persistent Memory Support Describes and shows how to use libpmem from the PMDK, a low-level library providing persistent memory support.

- Chapter 7. libpmemobj: A Native Transactional Object Store Provides information and examples using libpmemobj, a C native object store library from the PMDK.

- Chapter 8. libpmemobj-cpp: The Adaptable Language C++ and Persistent Memory – *Demonstrates the C++ libpmemobj-cpp object store from the PMDK, built using C++ headers on top of libpmemobj.*

- Chapter 9. pmemkv: A Persistent In-Memory Key-Value Store Expands upon the introduction to libpmemkv from Chapter 1 with a more in-depth discussion using examples.

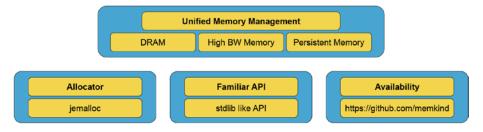

- Chapter 10. Volatile Use of Persistent Memory This chapter is for those who want to take advantage of persistent memory but do not require data to be stored persistently. libmemkind is a userextensible heap manager built on top of jemalloc which enables control of memory characteristics and a partitioning of the heap

#### PREFACE

between different kinds of memory, including persistent memory. libvmemcache is an embeddable and lightweight in-memory caching solution. It is designed to fully take advantage of large-capacity memory, such as persistent memory with DAX, through memory mapping in an efficient and scalable way.

- Chapter 11. Designing Data Structures for Persistent Memory Provides a wealth of information for designing data structures for persistent memory.

- Chapter 12. Debugging Persistent Memory Applications *Introduces tools and walks through several examples for how software developers can debug persistent memory-enabled applications.*

- Chapter 13. Enabling Persistence using a Real-World Application *Discusses how a real-world application was modified to enable persistent memory features.*

- Chapter 14. Concurrency and Persistent Memory *Describes how concurrency in applications should be implemented for use with persistent memory.*

- Chapter 15. Profiling and Performance *Teaches performance* concepts and demonstrates how to use the Intel VTune suite of tools to profile systems and applications before and after code changes are made.

- Chapter 16. PMDK Internals: Important Algorithms and Data Structures – *Takes us on a deep dive of the PMDK design, architecture, algorithms, and memory allocator implementation.*

- Chapter 17. Reliability, Availability, and Serviceability (RAS) Describes the implementation of reliability, availability, and serviceability (RAS) with the hardware and operating system layers.

- Chapter 18. Remote Persistent Memory *Discusses how applications* can scale out across multiple systems using local and remote persistent memory.

- Chapter 19. Advanced Topics *Describes things such as NUMA, using software volume managers, and the mmap() MAP\_SYNC flag.*

The Appendixes have separate procedures for installing the PMDK and utilities required for managing persistent memory. We also included an update for Java and the future of the RDMA protocols. All of this content is considered temporal, so we did not want to include it in the main body of the book.

### **Intended Audience**

This book has been written for experienced application developers in mind. We intend the content to be useful to a wider readership such as system administrators and architects, students, lecturers, and academic research fellows to name but a few. System designers, kernel developers, and anyone with a vested or passing interest in this emerging technology will find something useful within this book.

Every reader will learn what persistent memory is, how it works, and how operating systems and applications can utilize it. Provisioning and managing persistent memory are vendor specific, so we include some resources in the Appendix sections to avoid overcomplicating the main chapter content.

Application developers will learn, by example, how to integrate persistent memory in to existing or new applications. We use examples extensively throughout this book using a variety of libraries available within the Persistent Memory Development Kit (PMDK). Example code is provided in a variety of programming languages such as C, C++, JavaScript, and others. We want developers to feel comfortable using these libraries in their own projects. The book provides extensive links to resources where you can find help and information.

System administrators and architects of Cloud, high-performance computing, and enterprise environments can use most of the content of this book to understand persistent memory features and benefits to support applications and developers. Imagine being able to deploy more virtual machines per physical server or provide applications with this new memory/storage tier such that they can keep more data closer to the CPU or restart in a fraction of the time they could before while keeping a warm cache of data.

Students, lecturers, and academic research fellows will also benefit from many chapters within this book. Computer science classes can learn about the hardware, operating system features, and programming techniques. Lecturers are free use the content in student classes or to form the basis of research projects such as new persistent memory file systems, algorithms, or caching implementations. PREFACE

We introduce tools that profile the server and applications to better understand CPU, memory, and disk IO access patterns. Using this knowledge, we show how applications can be modified to take full advantage of persistence using the Persistent Memory Development Kit (PMDK).

### **A Future Reference**

The book content has been written to provide value for many years. Industry specification such as ACPI, UEFI, and the SNIA non-volatile programming model will, unless otherwise stated by the specification, remain backward compatible as new versions are released. If new form factors are introduced, the approach to programming remains the same. We do not limit ourselves to one specific persistent memory vendor or implementation. In places where it is necessary to describe vendor-specific features or implementations, we specifically call this out as it may change between vendors or between product generations. We encourage you to read the vendor documentation for the persistent memory product to learn more.

Developers using the Persistent Memory Development Kit (PMDK) will retain a stable API interface. PMDK will deliver new features and performance improvements with each major release. It will evolve with new persistent memory products, CPU instructions, platform designs, industry specifications, and operating system feature support.

## **Source Code Examples**

Concepts and source code samples within this book adhere to the vendor neutral SNIA non-volatile memory programming model. SNIA which is the Storage Networking Industry Association is a non-profit global organization dedicated to developing standards and education programs to advance storage and information technology. The model was designed, developed, and is maintained by the SNIA NVM Technical Working Group (TWG) which includes many leading operating system, hardware, and server vendors. You can join this group or find information at https://www.snia.org/forums/sssi/nvmp.

The code examples provided with this book have been tested and validated using Intel Optane DC persistent memory. Since the PMDK is vendor neutral, they will also work on NVDIMM-N devices. PMDK will support any future persistent memory product that enters the market.

The code examples used throughout this book are current at the time of publication. All code examples have been validated and tested to ensure they compile and execute without error. For brevity, some of the examples in this book use assert() statements to indicate unexpected errors. Any production code would likely replace these with the appropriate error handling actions which would include friendlier error messages and appropriate error recovery actions. Additionally, some of the code examples use different mount points to represent persistent memory aware file systems, for example "/daxfs", "/pmemfs", and "/mnt/pmemfs". This demonstrates persistent memory file systems can be mounted and named appropriately for the application, just like regular block-based file systems. Source code is from the repository that accompanies this book – https://github.com/Apress/programming-persistent-memory.

Since this is a rapidly evolving technology, the software and APIs references throughout this book may change over time. While every effort is made to be backward compatible, sometimes software must evolve and invalidate previous versions. For this reason, it is therefore expected that some of the code samples may not compile on newer hardware or operating systems and may need to be changed accordingly.

# **Book Conventions**

This book uses several conventions to draw your attention to specific pieces of information. The convention used depends on the type of information displayed.

### **Computer Commands**

Commands, programming library, and API function references may be presented in line with the paragraph text using a monospaced font. For example:

To illustrate how persistent memory is used, let's start with a sample program demonstrating the key-value store provided by a library called libpmemkv.

PREFACE

### **Computer Terminal Output**

Computer terminal output is usually taken directly from a computer terminal presented in a monospaced font such as the following example demonstrating cloning the Persistent Memory Development Kit (PMDK) from the GitHub project:

```

$ git clone https://github.com/pmem/pmdk

Cloning into 'pmdk'...

remote: Enumerating objects: 12, done.

remote: Counting objects: 100% (12/12), done.

remote: Compressing objects: 100% (10/10), done.

remote: Total 100169 (delta 2), reused 7 (delta 2), pack-reused 100157

Receiving objects: 100% (100169/100169), 34.71 MiB | 4.85 MiB/s, done.

Resolving deltas: 100% (83447/83447), done.

```

### **Source Code**

Source code examples taken from the accompanying GitHub repository are shown with relevant line numbers in a monospaced font. Below each code listing is a reference to the line number or line number range with a brief description. Code comments use language native styling. Most languages use the same syntax. Single line comments will use // and block/multiline comments should use /\*..\*/. An example is shown in Listing 1.

Listing 1. A sample program using libpmemkv

```

#include <iostream>

37

#include "libpmemkv.h"

38

39

40

using namespace pmemkv;

41

/*

42

43

* kvprint -- print a single key-value pair

*/

44

void kvprint(const string& k, const string& v) {

45

std::cout << "key: " << k << ", value: " << v << "\n";</pre>

46

47 }

```

• Line 45: Here we define a small helper routine, kvprint(), which prints a key-value pair when called.

### Notes

We use a standard format for notes, cautions, and tips when we want to direct your attention to an important point, for example.

**Note** Notes are tips, shortcuts, or alternative approaches to the current discussion topic. Ignoring a note should have no negative consequences, but you might miss out on a nugget of information that makes your life easier.

# **CHAPTER 1**

# Introduction to Persistent Memory Programming

This book describes programming techniques for writing applications that use persistent memory. It is written for experienced software developers, but we assume no previous experience using persistent memory. We provide many code examples in a variety of programming languages. Most programmers will understand these examples, even if they have not previously used the specific language.

**Note** All code examples are available on a GitHub repository (https://github.com/Apress/programming-persistent-memory), along with instructions for building and running it.

Additional documentation for persistent memory, example programs, tutorials, and details on the Persistent Memory Development Kit (PMDK), which is used heavily in this book, can be found on http://pmem.io.

The persistent memory products on the market can be used in various ways, and many of these ways are transparent to applications. For example, all persistent memory products we encountered support the storage interfaces and standard file API's just like any solid-state disk (SSD). Accessing data on an SSD is simple and well-understood, so we consider these use cases outside the scope of this book. Instead, we concentrate on memory-style access, where applications manage byte-addressable data structures that reside in persistent memory. Some use cases we describe are *volatile*, using the persistent memory only for its capacity and ignoring the fact it is persistent. However, most of this book is dedicated to the *persistent* use cases, where data structures placed in persistent memory are expected to survive crashes and power failures, and the techniques described in this book keep those data structures consistent across those events.

# A High-Level Example Program

To illustrate how persistent memory is used, we start with a sample program demonstrating the key-value store provided by a library called libpmemkv. Listing 1-1 shows a full C++ program that stores three key-value pairs in persistent memory and then iterates through the key-value store, printing all the pairs. This example may seem trivial, but there are several interesting components at work here. Descriptions below the listing show what the program does.

Listing 1-1. A sample program using libpmemkv

```

#include <iostream>

37

38 #include <cassert>

39 #include <libpmemkv.hpp>

40

41 using namespace pmem::kv;

42 using std::cerr;

43 using std::cout;

44 using std::endl;

using std::string;

45

46

/*

47

* for this example, create a 1 Gig file

48

* called "/daxfs/kvfile"

49

*/

50

auto PATH = "/daxfs/kvfile";

51

const uint64 t SIZE = 1024 * 1024 * 1024;

52

53

54

/*

* kvprint -- print a single key-value pair

55

*/

56

int kvprint(string view k, string view v) {

57

58

cout << "key: " << k.data() <<</pre>

" value: " << v.data() << endl;</pre>

59

60

return 0;

61 }

62

```

```

63

int main() {

64

// start by creating the db object

db *kv = new db();

65

assert(kv != nullptr);

66

67

// create the config information for

68

// libpmemkv's open method

69

config cfg;

70

71

if (cfg.put string("path", PATH) != status::OK) {

72

cerr << pmemkv errormsg() << endl;</pre>

73

exit(1);

74

}

75

if (cfg.put uint64("force create", 1) != status::OK) {

76

cerr << pmemkv errormsg() << endl;</pre>

77

78

exit(1);

}

79

if (cfg.put uint64("size", SIZE) != status::OK) {

80

cerr << pmemkv errormsg() << endl;</pre>

81

82

exit(1);

}

83

84

85

86

// open the key-value store, using the cmap engine

if (kv->open("cmap", std::move(cfg)) != status::OK) {

87

cerr << db::errormsg() << endl;</pre>

88

89

exit(1);

}

90

91

// add some keys and values

92

if (kv->put("key1", "value1") != status::OK) {

93

cerr << db::errormsg() << endl;</pre>

94

exit(1);

95

}

96

```

```

97

if (kv->put("key2", "value2") != status::OK) {

98

cerr << db::errormsg() << endl;</pre>

exit(1);

99

100

}

if (kv->put("key3", "value3") != status::OK) {

101

cerr << db::errormsg() << endl;</pre>

102

103

exit(1);

104

}

105

106

// iterate through the key-value store, printing them

kv->get all(kvprint);

107

108

109

// stop the pmemkv engine

delete kv;

110

111

112

exit(0);

113 }

```

- Line 57: We define a small helper routine, kvprint(), which prints a key-value pair when called.

- Line 63: This is the first line of main() which is where every C++ program begins execution. We start by instantiating a key-value engine using the engine name "cmap". We discuss other engine types in Chapter 9.

- Line 70: The cmap engine takes config parameters from a config structure. The parameter "path" is configured to "/daxfs/kvfile", which is the path to a persistent memory file on a DAX file system; the parameter "size" is set to SIZE. Chapter 3 describes how to create and mount DAX file systems.

- Line 93: We add several key-value pairs to the store. The trademark of a key-value store is the use of simple operations like put() and get(); we only show put() in this example.

- Line 107: Using the get\_all() method, we iterate through the entire key-value store, printing each pair when get\_all() calls our kvprint() routine.

# What's Different?

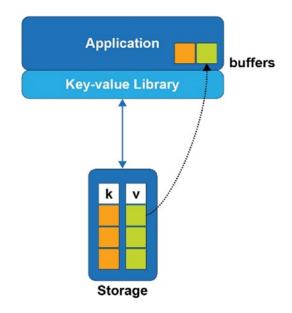

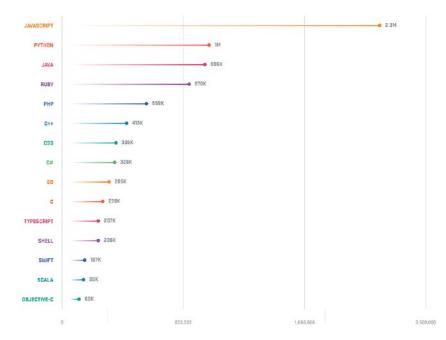

A wide variety of key-value libraries are available in practically every programming language. The persistent memory example in Listing 1-1 is different because the key-value store itself resides in persistent memory. For comparison, Figure 1-1 shows how a key-value store using traditional storage is laid out.

Figure 1-1. A key-value store on traditional storage

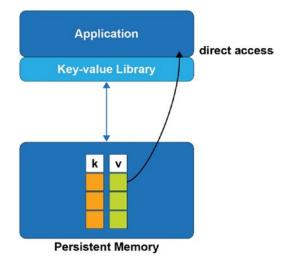

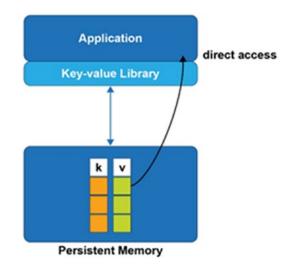

When the application in Figure 1-1 wants to fetch a value from the key-value store, a buffer must be allocated in memory to hold the result. This is because the values are kept on block storage, which cannot be addressed directly by the application. The only way to access a value is to bring it into memory, and the only way to do that is to read full blocks from the storage device, which can only be accessed via block I/O. Now consider Figure 1-2, where the key-value store resides in persistent memory like our sample code.

#### CHAPTER 1 INTRODUCTION TO PERSISTENT MEMORY PROGRAMMING

#### Figure 1-2. A key-value store in persistent memory

With the persistent memory key-value store, values are accessed by the application directly, without the need to first allocate buffers in memory. The kvprint() routine in Listing 1-1 will be called with references to the actual keys and values, directly where they live in persistence – something that is not possible with traditional storage. In fact, even the data structures used by the key-value store library to organize its data are accessed directly. When a storage-based key-value store library needs to make a small update, for example, 64 bytes, it must read the block of storage containing those 64 bytes into a memory buffer, update the 64 bytes, and then write out the entire block to make it persistent. That is because storage accesses can only happen using block I/O, typically 4K bytes at a time, so the task to update 64 bytes requires reading 4K and then writing 4K. But with persistent memory, the same example of changing 64 bytes would only write the **64 bytes directly to persistence**.

### **The Performance Difference**

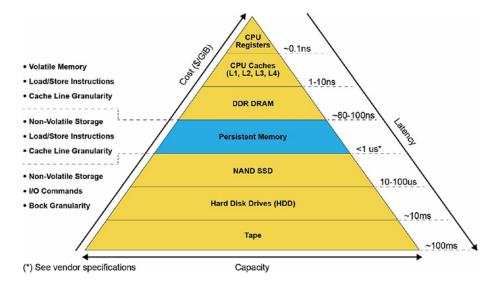

Moving a data structure from storage to persistent memory does not just mean smaller I/O sizes are supported; there is a fundamental performance difference. To illustrate this, Figure 1-3 shows a hierarchy of latency among the different types of media where data can reside at any given time in a program.

#### CHAPTER 1 INTRODUCTION TO PERSISTENT MEMORY PROGRAMMING

Figure 1-3. The memory/storage hierarchy pyramid with estimated latencies

As the pyramid shows, persistent memory provides latencies similar to memory, measured in nanoseconds, while providing persistency. Block storage provides persistency with latencies starting in the microseconds and increasing from there, depending on the technology. Persistent memory is unique in its ability to act like both memory and storage at the same time.

# **Program Complexity**

Perhaps the most important point of our example is that the programmer still uses the familiar get/put interfaces normally associated with key-value stores. The fact that the data structures are in persistent memory is abstracted away by the high-level API provided by libpmemkv. This principle of using the highest level of abstraction possible, as long as it meets the application's needs, will be a recurring theme throughout this book. We start by introducing very high-level APIs; later chapters delve into the lowerlevel details for programmers who need them. At the lowest level, programming directly to raw persistent memory requires detailed knowledge of things like hardware atomicity, cache flushing, and transactions. High-level libraries like libpmemkv abstract away all that complexity and provide much simpler, less error-prone interfaces.

### **How Does libpmemkv Work?**

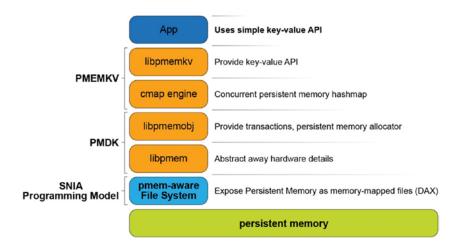

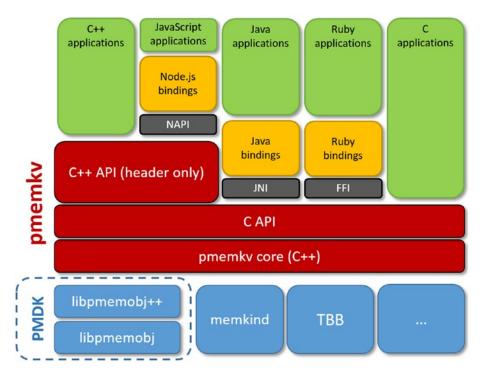

All the complexity hidden by high-level libraries like libpmemkv are described more fully in later chapters, but let's look at the building blocks used to construct a library like this. Figure 1-4 shows the full software stack involved when an application uses libpmemkv.

Figure 1-4. The software stack when using libpmemkv

Starting from the bottom of Figure 1-4 and working upward are these components:

- The *persistent memory* hardware, typically connected to the system memory bus and accessed using common memory load/store operations.

- A *pmem-aware file system*, which is a kernel module that exposes persistent memory to applications as files. Those files can be memory mapped to give applications direct access (abbreviated as DAX). This method of exposing persistent memory was published by SNIA (Storage Networking Industry Association) and is described in detail in Chapter 3.

- The libpmem library is part of the PMDK. This library abstracts away some of the low-level hardware details like cache flushing instructions.

- The libpmemobj library is a full-featured transaction and allocation library for persistent memory. (Chapters 7 and 8 describe libpmemobj and its C++ cousin in more detail.) If you cannot find data structures that meet your needs, you will most likely have to implement what you need using this library, as described in Chapter 11.

- The *cmap* engine, a concurrent hash map optimized for persistent memory.

- The libpmemkv library, providing the API demonstrated in Listing 1-1.

- And finally, the application that uses the API provided by libpmemkv.

Although there is quite a stack of components in use here, it does not mean there is necessarily a large amount of code that runs for each operation. Some components are only used during the initial setup. For example, the pmem-aware file system is used to find the persistent memory file and perform permission checks; it is out of the application's data path after that. The PMDK libraries are designed to leverage the direct access allowed by persistent memory as much as possible.

### What's Next?

Chapters 1 through 3 provide the essential background that programmers need to know to start persistent memory programming. The stage is now set with a simple example; the next two chapters provide details about persistent memory at the hardware and operating system levels. The later and more advanced chapters provide much more detail for those interested.

Because the immediate goal is to get you programming quickly, we recommend reading Chapters 2 and 3 to gain the essential background and then dive into Chapter 4 where we start to show more detailed persistent memory programming examples.

# Summary

This chapter shows how high-level APIs like libpmemkv can be used for persistent memory programming, hiding complex details of persistent memory from the application developer. Using persistent memory can allow finer-grained access and higher performance than block-based storage. We recommend using the highest-level, simplest APIs possible and only introducing the complexity of lower-level persistent memory programming as necessary.

#### CHAPTER 1 INTRODUCTION TO PERSISTENT MEMORY PROGRAMMING

**Open Access** This chapter is licensed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.

org/licenses/by/4.0/), which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this chapter are included in the chapter's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the chapter's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

### **CHAPTER 2**

# Persistent Memory Architecture

This chapter provides an overview of the persistent memory architecture while focusing on the hardware to emphasize requirements and decisions that developers need to know.

Applications that are designed to recognize the presence of persistent memory in a system can run much faster than using other storage devices because data does not have to transfer back and forth between the CPU and slower storage devices. Because applications that only use persistent memory may be slower than dynamic randomaccess memory (DRAM), they should decide what data resides in DRAM, persistent memory, and storage.

The capacity of persistent memory is expected to be many times larger than DRAM; thus, the volume of data that applications can potentially store and process in place is also much larger. This significantly reduces the number of disk I/Os, which improves performance and reduces wear on the storage media.

On systems without persistent memory, large datasets that cannot fit into DRAM must be processed in segments or streamed. This introduces processing delays as the application stalls waiting for data to be paged from disk or streamed from the network.

If the working dataset size fits within the capacity of persistent memory and DRAM, applications can perform in-memory processing without needing to checkpoint or page data to or from storage. This significantly improves performance.

# **Persistent Memory Characteristics**

As with every new technology, there are always new things to consider. Persistent memory is no exception. Consider these characteristics when architecting and developing solutions:

- Performance (throughput, latency, and bandwidth) of persistent memory is much better than NAND but potentially slower than DRAM.

- Persistent memory is durable unlike DRAM. Its endurance is usually orders of magnitude better than NAND and should exceed the lifetime of the server without wearing out.

- Persistent memory module capacities can be much larger than DRAM DIMMs and can coexist on the same memory channels.

- Persistent memory-enabled applications can update data in place without needing to serialize/deserialize the data.

- Persistent memory is byte addressable like memory. Applications can update only the data needed without any read-modify-write overhead.

- Data is CPU cache coherent.

- Persistent memory provides direct memory access (DMA) and remote DMA (RDMA) operations.

- Data written to persistent memory is not lost when power is removed.

- After permission checks are completed, data located on persistent memory is directly accessible from user space. No kernel code, file system page caches, or interrupts are in the data path.

- Data on persistent memory is instantly available, that is:

- Data is available as soon as power is applied to the system.

- Applications do not need to spend time warming up caches. They can access the data immediately upon memory mapping it.

- Data residing on persistent memory has no DRAM footprint unless the application copies data to DRAM for faster access.

- Data written to persistent memory modules is local to the system. Applications are responsible for replicating data across systems.

### **Platform Support for Persistent Memory**

Platform vendors such as Intel, AMD, ARM, and others will decide how persistent memory should be implemented at the lowest hardware levels. We try to provide a vendor-agnostic perspective and only occasionally call out platform-specific details.

For systems with persistent memory, failure atomicity guarantees that systems can always recover to a consistent state following a power or system failure. Failure atomicity for applications can be achieved using logging, flushing, and memory store barriers that order such operations. Logging, either undo or redo, ensures atomicity when a failure interrupts the last atomic operation from completion. Cache flushing ensures that data held within volatile caches reach the persistence domain so it will not be lost if a sudden failure occurs. Memory store barriers, such as an SFENCE operation on the x86 architecture, help prevent potential reordering in the memory hierarchy, as caches and memory controllers may reorder memory operations. For example, a barrier ensures that the undo log copy of the data gets persisted onto the persistent memory before the actual data is modified in place. This guarantees that the last atomic operation can be rolled back should a failure occur. However, it is nontrivial to add such failure atomicity in user applications with low-level operations such as write logging, cache flushing, and barriers. The Persistent Memory Development Kit (PMDK) was developed to isolate developers from having to re-implement the hardware intricacies.

Failure atomicity should be a familiar concept, since most file systems implement and perform journaling and flushing of their metadata to storage devices.

### **Cache Hierarchy**

We use load and store operations to read and write to persistent memory rather than using block-based I/O to read and write to traditional storage. We suggest reading the CPU architecture documentation for an in-depth description because each successive CPU generation may introduce new features, methods, and optimizations.

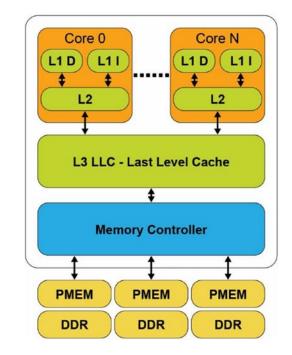

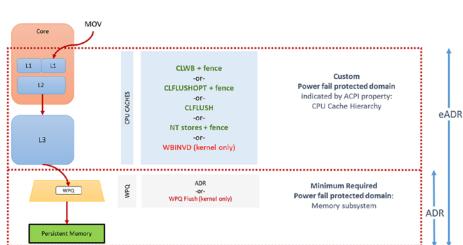

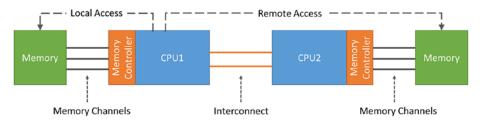

Using the Intel architecture as an example, a CPU cache typically has three distinct levels: L1, L2, and L3. The hierarchy makes references to the distance from the CPU core, its speed, and size of the cache. The L1 cache is closest to the CPU. It is extremely fast but very small. L2 and L3 caches are increasingly larger in capacity, but they are relatively slower. Figure 2-1 shows a typical CPU microarchitecture with three levels of CPU cache and a memory controller with three memory channels. Each memory channel has a single DRAM and persistent memory attached. On platforms where the CPU caches are not contained within the power-fail protected domain, any modified data within the CPU caches that has not been flushed to persistent memory will be lost when the system loses power or crashes. Platforms that do include CPU caches are flushed to the persistent memory should the system crash or loses power. We describe these requirements and features in the upcoming "Power-Fail Protected Domains" section.

#### Figure 2-1. CPU cache and memory hierarchy

The L1 (Level 1) cache is the fastest memory in a computer system. In terms of access priority, the L1 cache has the data the CPU is most likely to need while completing a specific task. The L1 cache is also usually split two ways, into the instruction cache (L1 I) and the data cache (L1 D). The instruction cache deals with the information about the operation that the CPU has to perform, while the data cache holds the data on which the operation is to be performed.

The L2 (Level 2) cache has a larger capacity than the L1 cache, but it is slower. L2 cache holds data that is likely to be accessed by the CPU next. In most modern CPUs, the L1 and L2 caches are present on the CPU cores themselves, with each core getting dedicated caches.

The L3 (Level 3) cache is the largest cache memory, but it is also the slowest of the three. It is also a commonly shared resource among all the cores on the CPU and may be internally partitioned to allow each core to have dedicated L3 resources.